ਡੀਆਈਪੀ ਨੂੰ ਸਮਝੋ

ਡੀਆਈਪੀ ਇੱਕ ਪਲੱਗ-ਇਨ ਹੈ। ਇਸ ਤਰੀਕੇ ਨਾਲ ਪੈਕ ਕੀਤੇ ਗਏ ਚਿਪਸ ਵਿੱਚ ਪਿੰਨਾਂ ਦੀਆਂ ਦੋ ਕਤਾਰਾਂ ਹੁੰਦੀਆਂ ਹਨ, ਜਿਨ੍ਹਾਂ ਨੂੰ ਸਿੱਧੇ ਡੀਆਈਪੀ ਢਾਂਚੇ ਵਾਲੇ ਚਿੱਪ ਸਾਕਟਾਂ ਨਾਲ ਵੈਲਡ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ ਜਾਂ ਇੱਕੋ ਜਿਹੇ ਛੇਕਾਂ ਵਾਲੇ ਵੈਲਡਿੰਗ ਸਥਾਨਾਂ 'ਤੇ ਵੈਲਡ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ। ਪੀਸੀਬੀ ਬੋਰਡ ਪਰਫੋਰੇਸ਼ਨ ਵੈਲਡਿੰਗ ਨੂੰ ਮਹਿਸੂਸ ਕਰਨਾ ਬਹੁਤ ਸੁਵਿਧਾਜਨਕ ਹੈ, ਅਤੇ ਮਦਰਬੋਰਡ ਨਾਲ ਚੰਗੀ ਅਨੁਕੂਲਤਾ ਹੈ, ਪਰ ਇਸਦੇ ਪੈਕੇਜਿੰਗ ਖੇਤਰ ਅਤੇ ਮੋਟਾਈ ਦੇ ਕਾਰਨ ਮੁਕਾਬਲਤਨ ਵੱਡਾ ਹੈ, ਅਤੇ ਸੰਮਿਲਨ ਅਤੇ ਹਟਾਉਣ ਦੀ ਪ੍ਰਕਿਰਿਆ ਵਿੱਚ ਪਿੰਨ ਨੂੰ ਨੁਕਸਾਨ ਪਹੁੰਚਾਉਣਾ ਆਸਾਨ ਹੈ, ਮਾੜੀ ਭਰੋਸੇਯੋਗਤਾ।

DIP ਸਭ ਤੋਂ ਪ੍ਰਸਿੱਧ ਪਲੱਗ-ਇਨ ਪੈਕੇਜ ਹੈ, ਐਪਲੀਕੇਸ਼ਨ ਰੇਂਜ ਵਿੱਚ ਸਟੈਂਡਰਡ ਲਾਜਿਕ IC, ਮੈਮੋਰੀ LSI, ਮਾਈਕ੍ਰੋਕੰਪਿਊਟਰ ਸਰਕਟ, ਆਦਿ ਸ਼ਾਮਲ ਹਨ। ਛੋਟਾ ਪ੍ਰੋਫਾਈਲ ਪੈਕੇਜ (SOP), SOJ (J-ਟਾਈਪ ਪਿੰਨ ਛੋਟਾ ਪ੍ਰੋਫਾਈਲ ਪੈਕੇਜ), TSOP (ਪਤਲਾ ਛੋਟਾ ਪ੍ਰੋਫਾਈਲ ਪੈਕੇਜ), VSOP (ਬਹੁਤ ਛੋਟਾ ਪ੍ਰੋਫਾਈਲ ਪੈਕੇਜ), SSOP (ਘਟਾਇਆ SOP), TSSOP (ਪਤਲਾ ਘਟਾਇਆ SOP) ਅਤੇ SOT (ਛੋਟਾ ਪ੍ਰੋਫਾਈਲ ਟਰਾਂਜ਼ਿਸਟਰ), SOIC (ਛੋਟਾ ਪ੍ਰੋਫਾਈਲ ਇੰਟੀਗ੍ਰੇਟਿਡ ਸਰਕਟ), ਆਦਿ ਤੋਂ ਲਿਆ ਗਿਆ ਹੈ।

ਡੀਆਈਪੀ ਡਿਵਾਈਸ ਅਸੈਂਬਲੀ ਡਿਜ਼ਾਈਨ ਨੁਕਸ

ਪੀਸੀਬੀ ਪੈਕੇਜ ਦਾ ਛੇਕ ਡਿਵਾਈਸ ਨਾਲੋਂ ਵੱਡਾ ਹੈ।

ਪੀਸੀਬੀ ਪਲੱਗ-ਇਨ ਛੇਕ ਅਤੇ ਪੈਕੇਜ ਪਿੰਨ ਛੇਕ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਦੇ ਅਨੁਸਾਰ ਬਣਾਏ ਗਏ ਹਨ। ਪਲੇਟ ਬਣਾਉਣ ਦੌਰਾਨ ਛੇਕਾਂ ਵਿੱਚ ਤਾਂਬੇ ਦੀ ਪਲੇਟਿੰਗ ਦੀ ਜ਼ਰੂਰਤ ਦੇ ਕਾਰਨ, ਆਮ ਸਹਿਣਸ਼ੀਲਤਾ ਪਲੱਸ ਜਾਂ ਘਟਾਓ 0.075mm ਹੈ। ਜੇਕਰ ਪੀਸੀਬੀ ਪੈਕੇਜਿੰਗ ਛੇਕ ਭੌਤਿਕ ਉਪਕਰਣ ਦੇ ਪਿੰਨ ਨਾਲੋਂ ਬਹੁਤ ਵੱਡਾ ਹੈ, ਤਾਂ ਇਹ ਉਪਕਰਣ ਦੇ ਢਿੱਲੇ ਹੋਣ, ਨਾਕਾਫ਼ੀ ਟੀਨ, ਏਅਰ ਵੈਲਡਿੰਗ ਅਤੇ ਹੋਰ ਗੁਣਵੱਤਾ ਸਮੱਸਿਆਵਾਂ ਵੱਲ ਲੈ ਜਾਵੇਗਾ।

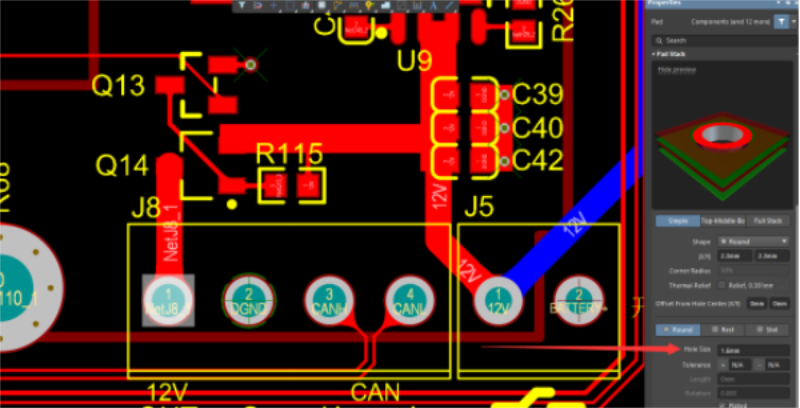

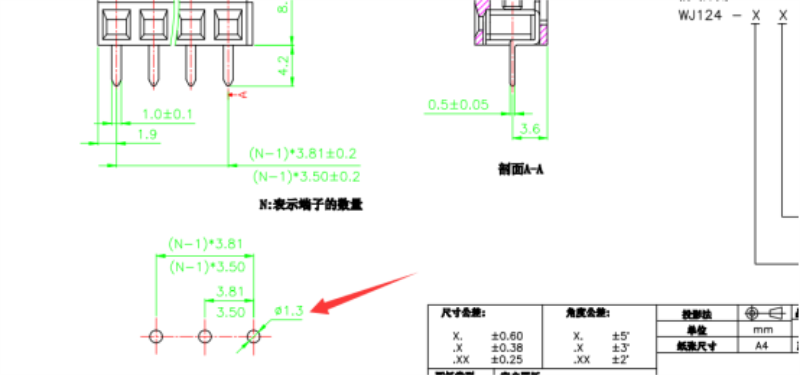

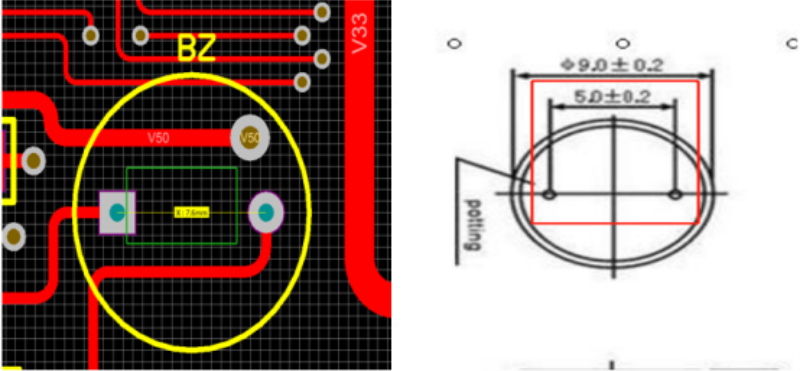

ਹੇਠਾਂ ਦਿੱਤਾ ਚਿੱਤਰ ਵੇਖੋ, WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ ਡਿਵਾਈਸ ਪਿੰਨ 1.3mm ਹੈ, PCB ਪੈਕੇਜਿੰਗ ਹੋਲ 1.6mm ਹੈ, ਅਪਰਚਰ ਬਹੁਤ ਵੱਡਾ ਹੈ ਓਵਰਵੇਵ ਵੈਲਡਿੰਗ ਸਪੇਸ ਟਾਈਮ ਵੈਲਡਿੰਗ ਲਈ ਲੀਡ ਹੈ।

ਚਿੱਤਰ ਨਾਲ ਨੱਥੀ ਕੀਤਾ ਗਿਆ ਹੈ, ਡਿਜ਼ਾਈਨ ਜ਼ਰੂਰਤਾਂ ਦੇ ਅਨੁਸਾਰ WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) ਕੰਪੋਨੈਂਟ ਖਰੀਦੋ, ਪਿੰਨ 1.3mm ਸਹੀ ਹੈ।

ਪੀਸੀਬੀ ਪੈਕੇਜ ਹੋਲ ਡਿਵਾਈਸ ਨਾਲੋਂ ਛੋਟਾ ਹੈ।

ਪਲੱਗ-ਇਨ, ਪਰ ਕੋਈ ਤਾਂਬਾ ਨਹੀਂ ਹੋਵੇਗਾ, ਜੇਕਰ ਇਹ ਸਿੰਗਲ ਹੈ ਅਤੇ ਡਬਲ ਪੈਨਲ ਇਸ ਵਿਧੀ ਦੀ ਵਰਤੋਂ ਕਰ ਸਕਦੇ ਹਨ, ਸਿੰਗਲ ਅਤੇ ਡਬਲ ਪੈਨਲ ਬਾਹਰੀ ਬਿਜਲੀ ਸੰਚਾਲਨ ਹਨ, ਸੋਲਡਰ ਸੰਚਾਲਕ ਹੋ ਸਕਦਾ ਹੈ; ਮਲਟੀਲੇਅਰ ਬੋਰਡ ਦਾ ਪਲੱਗ-ਇਨ ਮੋਰੀ ਛੋਟਾ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਪੀਸੀਬੀ ਬੋਰਡ ਨੂੰ ਸਿਰਫ ਤਾਂ ਹੀ ਦੁਬਾਰਾ ਬਣਾਇਆ ਜਾ ਸਕਦਾ ਹੈ ਜੇਕਰ ਅੰਦਰੂਨੀ ਪਰਤ ਵਿੱਚ ਬਿਜਲੀ ਸੰਚਾਲਨ ਹੋਵੇ, ਕਿਉਂਕਿ ਅੰਦਰੂਨੀ ਪਰਤ ਸੰਚਾਲਨ ਨੂੰ ਰੀਮਿੰਗ ਦੁਆਰਾ ਠੀਕ ਨਹੀਂ ਕੀਤਾ ਜਾ ਸਕਦਾ।

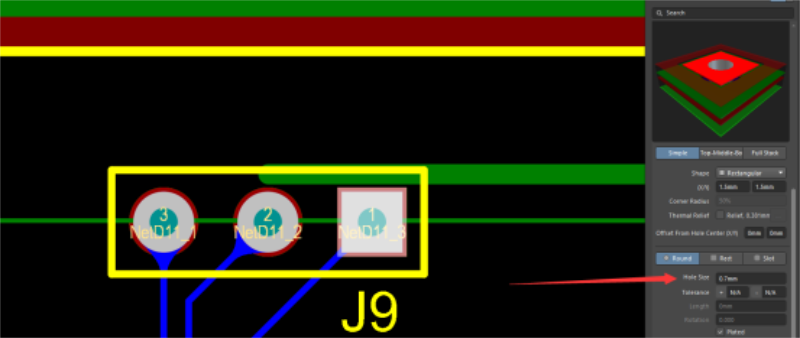

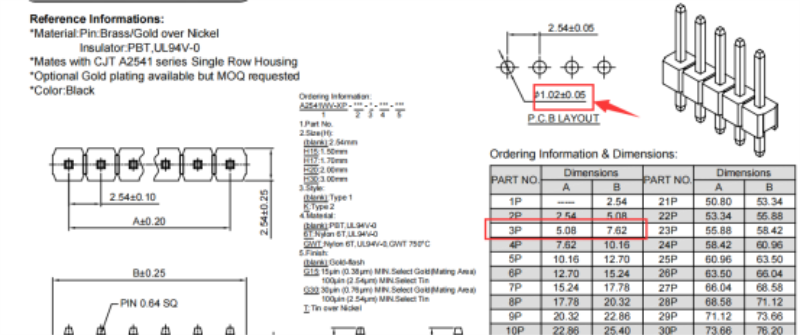

ਜਿਵੇਂ ਕਿ ਹੇਠਾਂ ਦਿੱਤੀ ਤਸਵੀਰ ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ, A2541Hwv-3P_A2541HWV-3P (CJT) ਦੇ ਹਿੱਸੇ ਡਿਜ਼ਾਈਨ ਜ਼ਰੂਰਤਾਂ ਦੇ ਅਨੁਸਾਰ ਖਰੀਦੇ ਗਏ ਹਨ। ਪਿੰਨ 1.0mm ਹੈ, ਅਤੇ PCB ਸੀਲਿੰਗ ਪੈਡ ਹੋਲ 0.7mm ਹੈ, ਜਿਸਦੇ ਨਤੀਜੇ ਵਜੋਂ ਪਾਉਣ ਵਿੱਚ ਅਸਫਲਤਾ ਹੁੰਦੀ ਹੈ।

A2541Hwv-3P_A2541HWV-3P (CJT) ਦੇ ਹਿੱਸੇ ਡਿਜ਼ਾਈਨ ਜ਼ਰੂਰਤਾਂ ਦੇ ਅਨੁਸਾਰ ਖਰੀਦੇ ਗਏ ਹਨ। ਪਿੰਨ 1.0mm ਸਹੀ ਹੈ।

ਪੈਕੇਜ ਪਿੰਨ ਸਪੇਸਿੰਗ ਡਿਵਾਈਸ ਸਪੇਸਿੰਗ ਤੋਂ ਵੱਖਰੀ ਹੈ

ਡੀਆਈਪੀ ਡਿਵਾਈਸ ਦੇ ਪੀਸੀਬੀ ਸੀਲਿੰਗ ਪੈਡ ਵਿੱਚ ਨਾ ਸਿਰਫ਼ ਪਿੰਨ ਦੇ ਬਰਾਬਰ ਅਪਰਚਰ ਹੁੰਦਾ ਹੈ, ਸਗੋਂ ਪਿੰਨ ਦੇ ਛੇਕਾਂ ਵਿਚਕਾਰ ਵੀ ਉਹੀ ਦੂਰੀ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਜੇਕਰ ਪਿੰਨ ਦੇ ਛੇਕਾਂ ਅਤੇ ਡਿਵਾਈਸ ਵਿਚਕਾਰ ਦੂਰੀ ਅਸੰਗਤ ਹੈ, ਤਾਂ ਡਿਵਾਈਸ ਨੂੰ ਨਹੀਂ ਪਾਇਆ ਜਾ ਸਕਦਾ, ਸਿਵਾਏ ਐਡਜਸਟੇਬਲ ਫੁੱਟ ਸਪੇਸਿੰਗ ਵਾਲੇ ਹਿੱਸਿਆਂ ਦੇ।

ਜਿਵੇਂ ਕਿ ਹੇਠਾਂ ਦਿੱਤੀ ਤਸਵੀਰ ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ, PCB ਪੈਕੇਜਿੰਗ ਦੀ ਪਿੰਨ ਹੋਲ ਦੂਰੀ 7.6mm ਹੈ, ਅਤੇ ਖਰੀਦੇ ਗਏ ਹਿੱਸਿਆਂ ਦੀ ਪਿੰਨ ਹੋਲ ਦੂਰੀ 5.0mm ਹੈ। 2.6mm ਦਾ ਅੰਤਰ ਡਿਵਾਈਸ ਨੂੰ ਵਰਤੋਂ ਯੋਗ ਨਹੀਂ ਬਣਾਉਂਦਾ।

ਪੀਸੀਬੀ ਪੈਕੇਜਿੰਗ ਛੇਕ ਬਹੁਤ ਨੇੜੇ ਹਨ।

ਪੀਸੀਬੀ ਡਿਜ਼ਾਈਨ, ਡਰਾਇੰਗ ਅਤੇ ਪੈਕੇਜਿੰਗ ਵਿੱਚ, ਪਿੰਨ ਹੋਲਾਂ ਵਿਚਕਾਰ ਦੂਰੀ ਵੱਲ ਧਿਆਨ ਦੇਣਾ ਜ਼ਰੂਰੀ ਹੈ। ਭਾਵੇਂ ਨੰਗੀ ਪਲੇਟ ਤਿਆਰ ਕੀਤੀ ਜਾ ਸਕਦੀ ਹੈ, ਪਿੰਨ ਹੋਲਾਂ ਵਿਚਕਾਰ ਦੂਰੀ ਛੋਟੀ ਹੈ, ਵੇਵ ਸੋਲਡਰਿੰਗ ਦੁਆਰਾ ਅਸੈਂਬਲੀ ਦੌਰਾਨ ਟੀਨ ਸ਼ਾਰਟ ਸਰਕਟ ਦਾ ਕਾਰਨ ਬਣਨਾ ਆਸਾਨ ਹੈ।

ਜਿਵੇਂ ਕਿ ਹੇਠਾਂ ਦਿੱਤੀ ਤਸਵੀਰ ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ, ਸ਼ਾਰਟ ਸਰਕਟ ਛੋਟੀ ਪਿੰਨ ਦੂਰੀ ਕਾਰਨ ਹੋ ਸਕਦਾ ਹੈ। ਸੋਲਡਰਿੰਗ ਟੀਨ ਵਿੱਚ ਸ਼ਾਰਟ ਸਰਕਟ ਦੇ ਕਈ ਕਾਰਨ ਹਨ। ਜੇਕਰ ਡਿਜ਼ਾਈਨ ਦੇ ਅੰਤ ਵਿੱਚ ਅਸੈਂਬਲੀਬਿਲਟੀ ਨੂੰ ਪਹਿਲਾਂ ਤੋਂ ਰੋਕਿਆ ਜਾ ਸਕਦਾ ਹੈ, ਤਾਂ ਸਮੱਸਿਆਵਾਂ ਦੀ ਘਟਨਾ ਨੂੰ ਘਟਾਇਆ ਜਾ ਸਕਦਾ ਹੈ।

DIP ਡਿਵਾਈਸ ਪਿੰਨ ਸਮੱਸਿਆ ਦਾ ਮਾਮਲਾ

ਸਮੱਸਿਆ ਦਾ ਵੇਰਵਾ

ਇੱਕ ਉਤਪਾਦ ਡੀਆਈਪੀ ਦੀ ਵੇਵ ਕਰੈਸਟ ਵੈਲਡਿੰਗ ਤੋਂ ਬਾਅਦ, ਇਹ ਪਾਇਆ ਗਿਆ ਕਿ ਨੈੱਟਵਰਕ ਸਾਕਟ ਦੇ ਫਿਕਸਡ ਫੁੱਟ ਦੀ ਸੋਲਡਰ ਪਲੇਟ 'ਤੇ ਟੀਨ ਦੀ ਗੰਭੀਰ ਘਾਟ ਸੀ, ਜੋ ਕਿ ਏਅਰ ਵੈਲਡਿੰਗ ਨਾਲ ਸਬੰਧਤ ਸੀ।

ਸਮੱਸਿਆ ਦਾ ਪ੍ਰਭਾਵ

ਨਤੀਜੇ ਵਜੋਂ, ਨੈੱਟਵਰਕ ਸਾਕਟ ਅਤੇ PCB ਬੋਰਡ ਦੀ ਸਥਿਰਤਾ ਵਿਗੜ ਜਾਂਦੀ ਹੈ, ਅਤੇ ਉਤਪਾਦ ਦੀ ਵਰਤੋਂ ਦੌਰਾਨ ਸਿਗਨਲ ਪਿੰਨ ਫੁੱਟ ਦਾ ਬਲ ਲਗਾਇਆ ਜਾਵੇਗਾ, ਜੋ ਅੰਤ ਵਿੱਚ ਸਿਗਨਲ ਪਿੰਨ ਫੁੱਟ ਦੇ ਕਨੈਕਸ਼ਨ ਵੱਲ ਲੈ ਜਾਵੇਗਾ, ਉਤਪਾਦ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਕਰੇਗਾ ਅਤੇ ਉਪਭੋਗਤਾਵਾਂ ਦੀ ਵਰਤੋਂ ਵਿੱਚ ਅਸਫਲਤਾ ਦਾ ਜੋਖਮ ਪੈਦਾ ਕਰੇਗਾ।

ਸਮੱਸਿਆ ਐਕਸਟੈਂਸ਼ਨ

ਨੈੱਟਵਰਕ ਸਾਕਟ ਦੀ ਸਥਿਰਤਾ ਮਾੜੀ ਹੈ, ਸਿਗਨਲ ਪਿੰਨ ਦੀ ਕਨੈਕਸ਼ਨ ਕਾਰਗੁਜ਼ਾਰੀ ਮਾੜੀ ਹੈ, ਗੁਣਵੱਤਾ ਸਮੱਸਿਆਵਾਂ ਹਨ, ਇਸ ਲਈ ਇਹ ਉਪਭੋਗਤਾ ਲਈ ਸੁਰੱਖਿਆ ਜੋਖਮ ਲਿਆ ਸਕਦਾ ਹੈ, ਅੰਤਮ ਨੁਕਸਾਨ ਕਲਪਨਾਯੋਗ ਨਹੀਂ ਹੈ।

ਡੀਆਈਪੀ ਡਿਵਾਈਸ ਅਸੈਂਬਲੀ ਵਿਸ਼ਲੇਸ਼ਣ ਜਾਂਚ

ਡੀਆਈਪੀ ਡਿਵਾਈਸ ਪਿੰਨ ਨਾਲ ਸਬੰਧਤ ਬਹੁਤ ਸਾਰੀਆਂ ਸਮੱਸਿਆਵਾਂ ਹਨ, ਅਤੇ ਬਹੁਤ ਸਾਰੇ ਮੁੱਖ ਨੁਕਤਿਆਂ ਨੂੰ ਨਜ਼ਰਅੰਦਾਜ਼ ਕਰਨਾ ਆਸਾਨ ਹੈ, ਜਿਸਦੇ ਨਤੀਜੇ ਵਜੋਂ ਅੰਤਿਮ ਸਕ੍ਰੈਪ ਬੋਰਡ ਬਣ ਜਾਂਦਾ ਹੈ। ਤਾਂ ਫਿਰ ਅਜਿਹੀਆਂ ਸਮੱਸਿਆਵਾਂ ਨੂੰ ਇੱਕ ਵਾਰ ਅਤੇ ਹਮੇਸ਼ਾ ਲਈ ਜਲਦੀ ਅਤੇ ਪੂਰੀ ਤਰ੍ਹਾਂ ਕਿਵੇਂ ਹੱਲ ਕੀਤਾ ਜਾਵੇ?

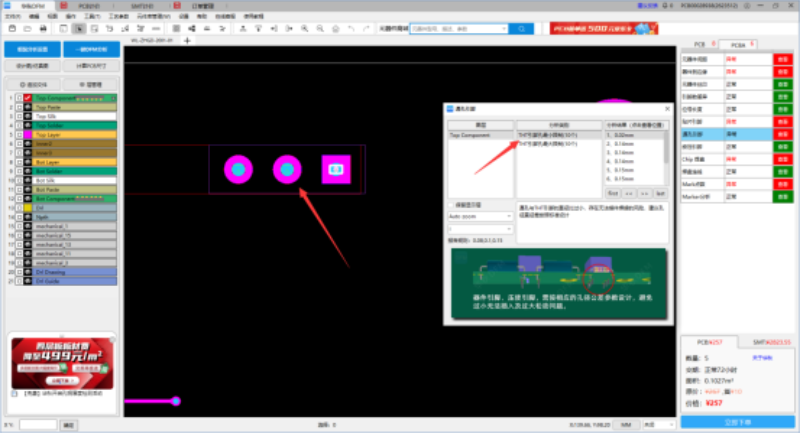

ਇੱਥੇ, ਸਾਡੇ CHIPSTOCK.TOP ਸੌਫਟਵੇਅਰ ਦੇ ਅਸੈਂਬਲੀ ਅਤੇ ਵਿਸ਼ਲੇਸ਼ਣ ਫੰਕਸ਼ਨ ਦੀ ਵਰਤੋਂ DIP ਡਿਵਾਈਸਾਂ ਦੇ ਪਿੰਨਾਂ 'ਤੇ ਵਿਸ਼ੇਸ਼ ਨਿਰੀਖਣ ਕਰਨ ਲਈ ਕੀਤੀ ਜਾ ਸਕਦੀ ਹੈ। ਨਿਰੀਖਣ ਆਈਟਮਾਂ ਵਿੱਚ ਛੇਕਾਂ ਰਾਹੀਂ ਪਿੰਨਾਂ ਦੀ ਗਿਣਤੀ, THT ਪਿੰਨਾਂ ਦੀ ਵੱਡੀ ਸੀਮਾ, THT ਪਿੰਨਾਂ ਦੀ ਛੋਟੀ ਸੀਮਾ ਅਤੇ THT ਪਿੰਨਾਂ ਦੀਆਂ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਸ਼ਾਮਲ ਹਨ। ਪਿੰਨਾਂ ਦੀਆਂ ਨਿਰੀਖਣ ਆਈਟਮਾਂ ਮੂਲ ਰੂਪ ਵਿੱਚ DIP ਡਿਵਾਈਸਾਂ ਦੇ ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਸੰਭਾਵਿਤ ਸਮੱਸਿਆਵਾਂ ਨੂੰ ਕਵਰ ਕਰਦੀਆਂ ਹਨ।

PCB ਡਿਜ਼ਾਈਨ ਦੇ ਪੂਰਾ ਹੋਣ ਤੋਂ ਬਾਅਦ, PCBA ਅਸੈਂਬਲੀ ਵਿਸ਼ਲੇਸ਼ਣ ਫੰਕਸ਼ਨ ਦੀ ਵਰਤੋਂ ਡਿਜ਼ਾਈਨ ਦੇ ਨੁਕਸ ਪਹਿਲਾਂ ਤੋਂ ਖੋਜਣ, ਉਤਪਾਦਨ ਤੋਂ ਪਹਿਲਾਂ ਡਿਜ਼ਾਈਨ ਵਿਗਾੜਾਂ ਨੂੰ ਹੱਲ ਕਰਨ, ਅਤੇ ਅਸੈਂਬਲੀ ਪ੍ਰਕਿਰਿਆ ਵਿੱਚ ਡਿਜ਼ਾਈਨ ਸਮੱਸਿਆਵਾਂ ਤੋਂ ਬਚਣ, ਉਤਪਾਦਨ ਦੇ ਸਮੇਂ ਵਿੱਚ ਦੇਰੀ ਕਰਨ ਅਤੇ ਖੋਜ ਅਤੇ ਵਿਕਾਸ ਲਾਗਤਾਂ ਨੂੰ ਬਰਬਾਦ ਕਰਨ ਲਈ ਕੀਤੀ ਜਾ ਸਕਦੀ ਹੈ।

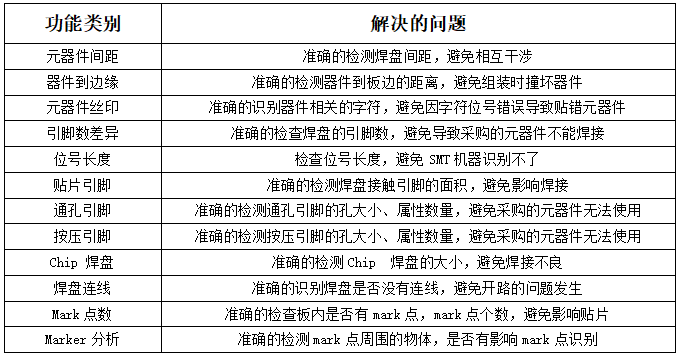

ਇਸਦੇ ਅਸੈਂਬਲੀ ਵਿਸ਼ਲੇਸ਼ਣ ਫੰਕਸ਼ਨ ਵਿੱਚ 10 ਪ੍ਰਮੁੱਖ ਆਈਟਮਾਂ ਅਤੇ 234 ਵਧੀਆ ਆਈਟਮਾਂ ਦੇ ਨਿਰੀਖਣ ਨਿਯਮ ਹਨ, ਜੋ ਸਾਰੀਆਂ ਸੰਭਾਵਿਤ ਅਸੈਂਬਲੀ ਸਮੱਸਿਆਵਾਂ ਨੂੰ ਕਵਰ ਕਰਦੇ ਹਨ, ਜਿਵੇਂ ਕਿ ਡਿਵਾਈਸ ਵਿਸ਼ਲੇਸ਼ਣ, ਪਿੰਨ ਵਿਸ਼ਲੇਸ਼ਣ, ਪੈਡ ਵਿਸ਼ਲੇਸ਼ਣ, ਆਦਿ, ਜੋ ਕਈ ਤਰ੍ਹਾਂ ਦੀਆਂ ਉਤਪਾਦਨ ਸਥਿਤੀਆਂ ਨੂੰ ਹੱਲ ਕਰ ਸਕਦੇ ਹਨ ਜਿਨ੍ਹਾਂ ਦਾ ਇੰਜੀਨੀਅਰ ਪਹਿਲਾਂ ਤੋਂ ਅੰਦਾਜ਼ਾ ਨਹੀਂ ਲਗਾ ਸਕਦੇ।

ਪੋਸਟ ਸਮਾਂ: ਜੁਲਾਈ-05-2023